1.基本概念

总线,bus,表示计算机内各元器件之间的共享的传输介质,如大脑中的神经系统什么是总线

总线是连接各个部件的信息传输线,是各个部件共享的传输介质,是计算机各种功能之间传送信息的公共通信干线,由导线组成。

总线是分位的,目前电脑的总线位数由16位、32位、64位等。位数越大,传输数据越多,越快。

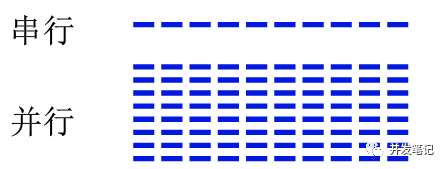

总线上的信息传送

- 串行

- 并行

图0812-1 串行并行示意图

总线结构图示

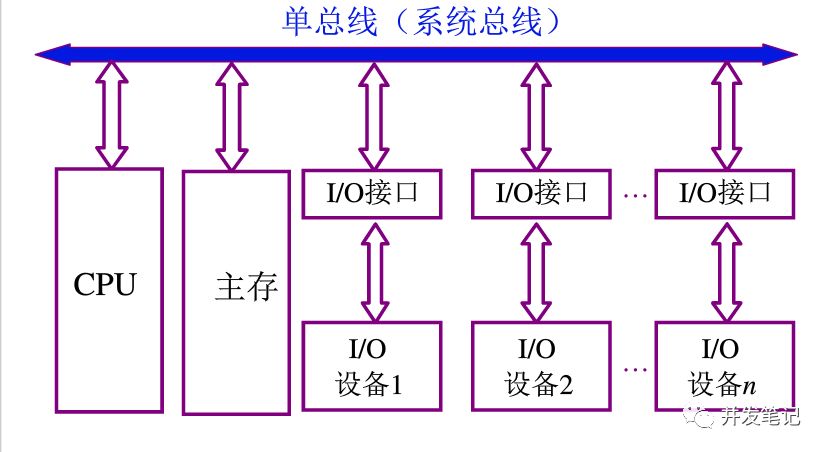

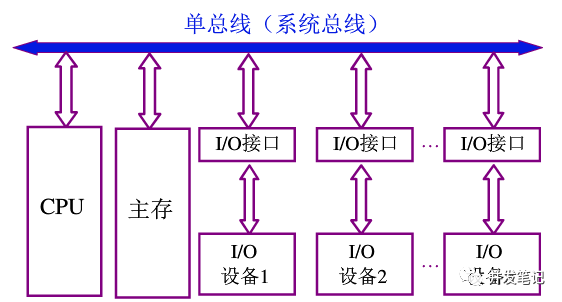

单总线结构

单总线结构 所有I/O设备都挂载在同一个系统总线上

优点:简单,易于扩展

缺点:总线共用,易阻塞

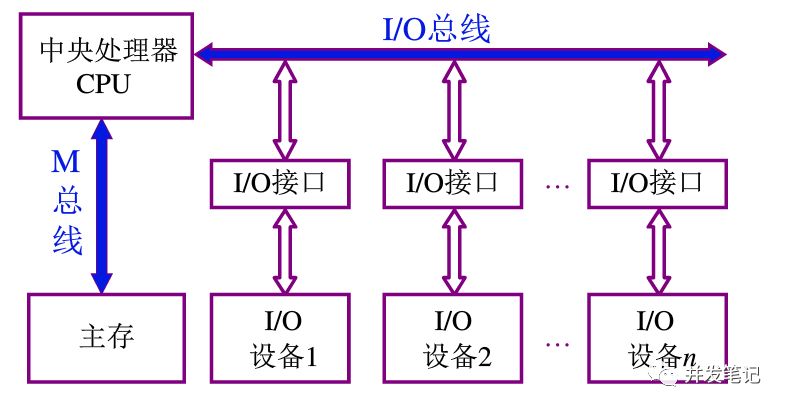

面向CPU的双总线结构

以CPU为中心,I/O总线连接所有外部输入输出设备,M总线连接系统主存

优点:实践表明,CPU与主存之间通信最为频繁,所以在CPU与主存之间加一条单独总线尤为重要,提高系统的效率

缺点:结构较为复杂,当I/O设备需要与主存通信时,需要进过CPU转发,加大了CPU的负载

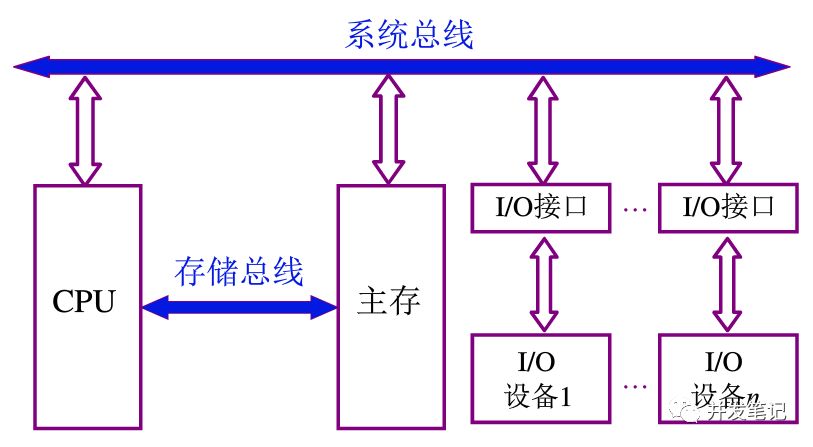

以主存为中心的双总线结构

在以CPU为中心的双总线结构之上,将主存连接在系统总线之上

2.总线分类

以位置区分

片内总线: 芯片内部的总线 系统总线: 计算机内各部件之间的信息传输线 数据总线:双向,与机器字长、存储字长有关 地址总线:单向,与存储地址、I/O地址有关 控制总线

通信总线: 计算机之间或计算机系统与其他系统之间通信

传输方式: 串行通信总线、并行通信总线

以功能区分

数据总线

用以传输数据地址总线

用以传输数据地址

控制总线

用以传输控制信号

3.总线特性及性能指标

3.1总线物理实现

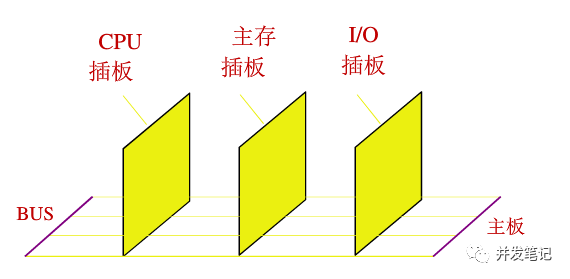

图0811-2 总线物理结构示意图

3.2总线特性

从物理角度来看,总线由许多导线直接印在电路板上,延伸到各个部件机械特性

总线在机械连接方式上的一些性能,如插头与插座使用的标准,几何尺寸、形状、引脚的个数以及排列的顺序,接头处的可靠接触等。

电气特性

总线每一根传输线上的信号的传递方向和有效的电平范围。通常规定由CPU发出的信号称为输出信号,送入CPU的型号称为输入信号。

通常,由主设备(如CPU)发出的信号称为输出信号(OUT),送入主设备的信号称为输入信号(IN)。

通常数据信号和地址信号定义高电平为逻辑1、低电平为逻辑0

控制信号则没有俗成的约定,如WE表示低电平有效、Ready表示高电平有效。

不同总线高电平、低电平的电平范围也无统一的规定,大多数总线的电平定义与TTL(TTL规定,+5V等价于逻辑"1",0V等价于逻辑"0")相符,例外情况,如RS-232C(串行总线接口标准)其电平特性规定低电平表示逻辑"1",并要求电平低于-3V;用高电平表示逻辑"0",还要求高电平需高于+3V,额定信号电平位-10V和+10V左右。功能特性

传输线的功能:地址(地址码)/数据(数据)/控制(操作命令、状态)

地址总线-指出地址码

数据总线-传递数据

控制总线-发出控制信号时间特性

信号的时序关系

时间特性又称为逻辑特性,指在总线操作过程中每一根信号线上信号什么时候有效,通过这种信号有效的时序关系约定,确保了总线操作的正确进行。

3.3总线性能指标

总线宽度

数据线的根数,用bit(位)来表示

8位 - 8根

16位 - 16根

32位 - 32根

64位 - 64根总线带宽:表示总线的数据传输速率,即单位时间内总线上传输数据的位数,用每秒传输信息的字节数来衡量,单位MBps(兆字节每秒)MHz × (W ÷ 8) = 1 MBps

- MBps 总线带宽,即标准传输率

- MHz 总线工作频率

- W 总线宽度

- 8 一字节相当于8位二进制数

时钟同步/异步

同步、不同步

总线上的数据与时钟同步工作的总线称为同步总线,与时钟不同步工作的总线称为异同步总线。总线复用

地址线与数据线的公用,其目的是减少引脚数

信号线数

地址线/数据线和控制线的总和

总线控制方式

突发

自动

仲裁

逻辑

计数

其他指标

负载能力

总线的负载能力即驱动能力,是指当总线接上负载后,总线输入输出的逻辑电平是否能保持在正常的额定范围内

3.4总线标准

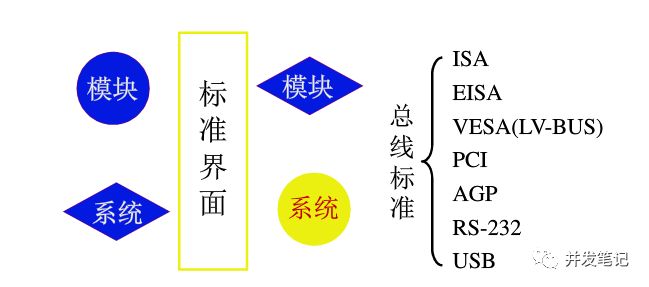

总线标准:系统与各模块、模块与模块之间的一个互联的标准界面

图0811-3 总线标准示意

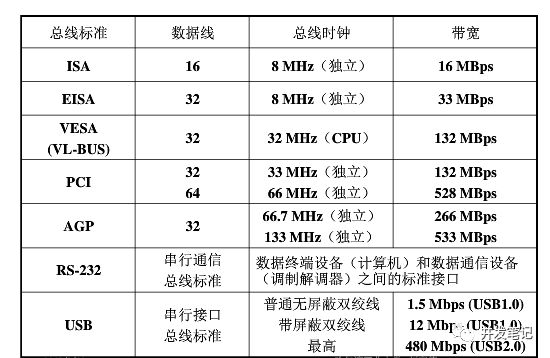

图0811-4 总线标准

标准说明

- ISA总线(Industrial Standard Architecture) IBM为了采用全16位的CPU而推出的,又称为AT总线。由于其没有支持总线仲裁的硬件逻辑,因此不能支持堕胎住设备系统。

- EISA总线(Extended Industrial Standard Architecture) 在ISA基础上扩充开放的总线标准。

- VESA(VL-BUS)总线 由VESA(Video Electronic Standard Association,视频电子协会标准)提出的局部总线(在系统外为两个以上模块提供的高速传输信息通道)标准。

- PCI总线(Peripheral ComponentInterconnect,外围部件互连) 随着图形用户接口(Graphical User Interface,GUI)和多媒体技术在PC系统上的广泛应用而应运而生的总线。 PCI总线具有以下特点: - 高性能 - 良好的兼容性 - 支持即插即用(Plug and Play) - 支持多主设备能力 - 具有与处理器和存储器子系统完全并行操作的能力 - 提供数据和地址奇偶校验功能 - 支持两种电压标准 - 可扩充性好 - 软件兼容性好 - 采用多路符合技术,减少了总线引脚个数

- AGP总线(Accelerated Graphics Port,加速图形端口) 随着多媒体计算机的普及,对三维技术的应用越来越广。Inter于1996年7月推出的,这是显示卡专用的局部总线,基于PCI2.1版规范并进行扩充修改而成。 AGP定义了一种"双激励"(Double Pumping)的传输技术,能在一个是助攻的上、下沿双向传递数据。

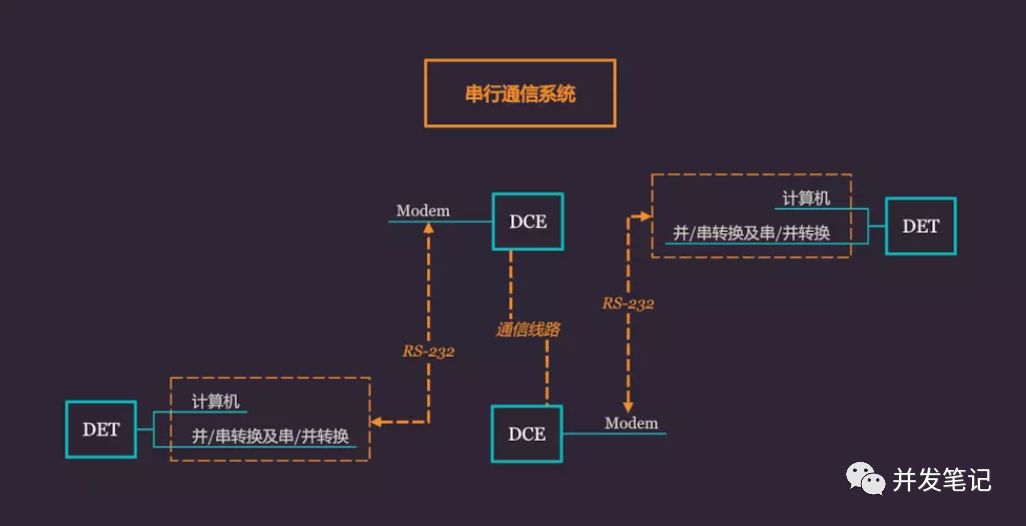

- RS-232C总线(Recommended Standard) 由国际电子工业协会EIA(Electronic Industries Association)推荐的一种串行通信总线标准,它是应用于串行二进制交换的数据终端设备(DTE)和数据通信设备(DCE)之间的标准接口。

图0811-3 串行通信系统

DTE(Data Terminal Equipment) 数据终端设备

DCE(Data Communication Equipment) 数据通信设备

Modem 调制解调器- USB总线(Universal Serial Bus)

通用串行总线。主要特点如下:

- 具有正真的即插即用特征 - 具有很强的连接能力 - 数据传输率有两种 - 标准统一 - 连接电缆轻巧,电源体积缩小 - 生命力强

4.总线结构

4.1单总线结构

代码语言:javascript复制

代码语言:javascript复制单总线结构:是一种将CPU、主存、I/O设备(通过I/O接口)都挂在一组总线上,允许I/O设备间、I/O设备与CPU之间或者I/O设备与主存之间直接交换形式的总线结构。

这种结构简单便于扩充,但所有的传送都是通过这组共享总线,极易形成计算机的性能瓶颈,因为总线不允许两个以上的部件在同一时刻向总线传输信息,这必然会影响系统工作效率的提高。

为了根本解决数据传输速率、解决CPU、主存与I/O设备之间传输速率的不匹配,实现CPU与其他设备相对同步,不得不采用多总线结构。

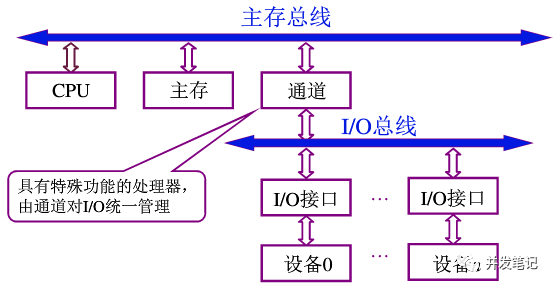

4.2双总线结构

双总线结构,将速度较低的I/O设备从单总线上分离出来,形成主存总线与I/O总线分开的结构。

通道:指一个具有特殊功能的处理器,CPU将一部分功能下方给通道,使其对I/O设备具备统一管理的功能,完成内外部设备与主存储器之前的数据传送。

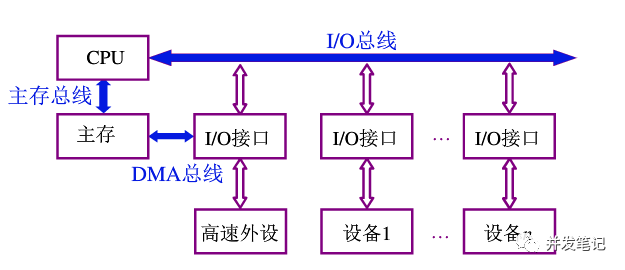

4.3三总线结构

结构一

将速率不同的I/O设备进行分类,然后将他们连接在不同的通道上,那么计算机系统的工作效率将会更高,由此发展成多总线结构,需要注意的是,在三总线结构中,任意时刻只能使用一种线

DMA总线:由主存连接高速I/O接口的总线

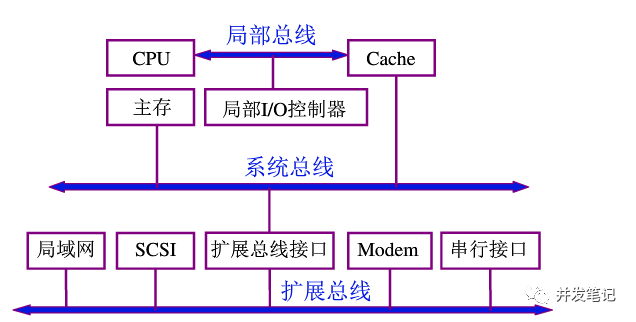

结构二

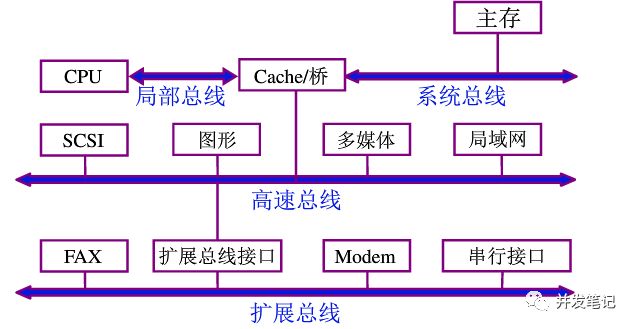

4.4四总线结构

在三总线的基础之上,增加了一条与计算机系统紧密相连的高速总线。在高速总线上挂接了一些高速I/O设备

这种结构对高速设备而言,其自身的工作可很少依赖CPU,同时他们又比扩展总线上的设备更贴近CPU,可见对于高性能设备与CPU来说,各自的效率将获得更大的提高。

4.5总线结构的实例

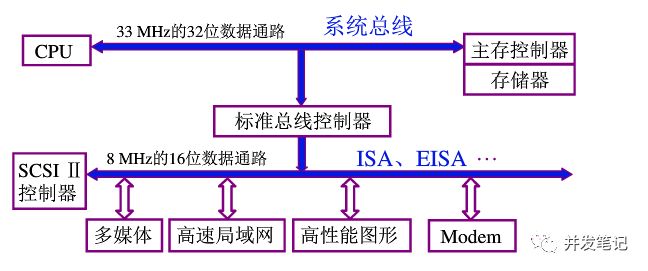

传统微型机总线结构

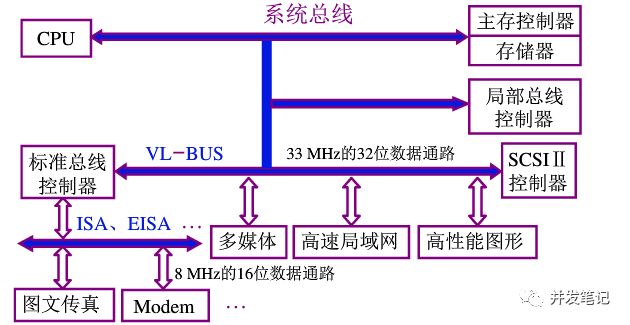

典型的双总线结构VL-BUS局部总线结构

将高速设备挂载在局部总线VL-Bus上,再与系统总线相连。

局部总线就相当于在CPU与高速I/O设备之间架上了高速通道,使CPU与高性能外设得到充分发挥,满足图形界面软件的需求

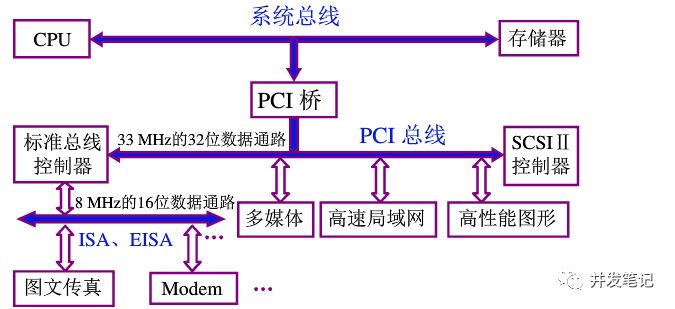

PCI结构总线

PCI总线是通过PCI桥路(包括PCI控制器和PCI加速器)与CPU纵向相连接。这种结构使CPU总线与CPI总线相互隔离,具有更高的灵活性,可以支持更多的高速运行设备,而且具有即插即用的特性

当PCI总线驱动能力不足时,可采用多层PCI结构

5.总线控制

总线在同一时刻,只能由一对设备使用

数据线:用于数据传输

地址线:用于从设备地址查找

5.1总线的判优控制

基本概念

- 主设备 对总线由控制权,可提出总线占用请求

- 从设备

5.2总线通信控制

目的

总线传输周期

- 申请分配阶段

- 寻址阶段

- 传数阶段

- 结束阶段

通信方式

- 同步通信

数据输入

数据输出 - 异步通信

- 半同步通信

- 分离式通信