主存与CPU的连接

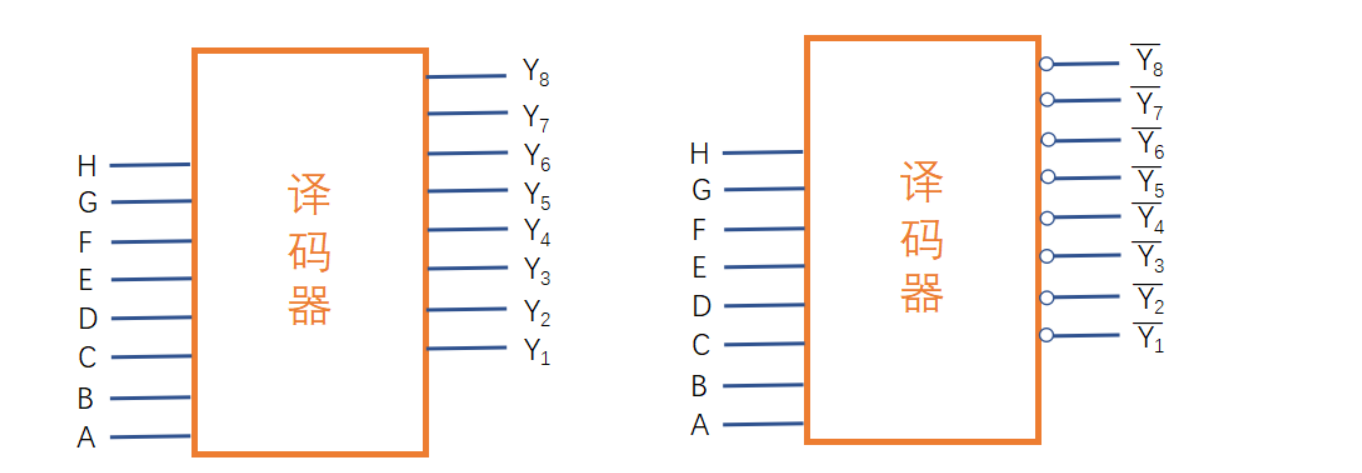

译码器

线选法

译码器

线选法

n条地址线线-> n个选片信号,电路简单,但是地址空间不连续

低电平有效:

输入电压为0,有效

输入电压为1,无效

译码片选法

译码片选法

n条地址线线->$2^n$个选片信号,电路复杂,但是地址空间连续

总结

线选法 | 译码片选法 |

|---|---|

n条地址线线->n个选片信号 | n条地址线线->$2^n$个选片信号 |

电路简单 | 电路复杂 |

地址空间不连续 | 地址空间可连续,可以增加逻辑设计 |

位拓展

位扩展:

假定手头只有若干 8Kx1位的SRAM芯片。首先需要使用2片该芯片,把这2片芯片连接为类似1片8Kx2位的芯片

可以看出,连接后存储单元数量不变,每个单元包含的位由1个变为2个,这种连接叫作存储器的位扩充。

位扩展

假定手头只有若干 8Kx1位的SRAM芯片首先需要使用8片该芯片,把这8片芯片连接为类似1片8Kx8位的芯片。

字拓展

字扩展:

假定手头只有若于 8Kx8位的SRAM芯片。首先需要使用2片该芯片,把这2片芯片连接为类似1片16Kx8位的芯片可以看出,连接后存储单元包含的位数不变,存储单元的数目增多。这种连接叫作地址(字)扩充。

线选法

片选法

字位同时拓展

主存提速方案

存储周期

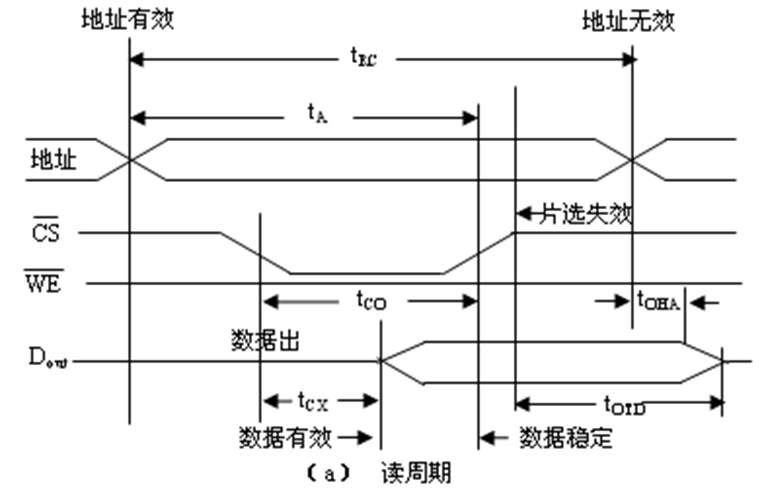

RAM读周期

读操作时,必须保证片选信号为低电平,读写信号为高电平。

$t_{RC}$ (读周期时间):指对芯片连续两次读操作之间的最小间隔时间。

$t_A$ (读出时间):从给出有效地址后,经过译码电路、驱动电路的延迟,到读出所选单元内容,并经I/O电路延迟,直到数据在外部数据总线上稳定出现所需的时间。显然,读出时间小于读周期时间。

$t{CO}$ (片选到数据输出稳定的时间):数据能否送到外部数据总线上,不仅取决于地址,还取决于片选信号。因此,$t{CO}$是从有效到数据稳定出现在外部数据总线上的时间。

$t_{CX}$(片选到数据输出有效时间):从片选有效到数据开始出现在数据总线上的间隔时间。

$t_{OTD}$:片选无效后数据还需在数据总线上保持的时间。

$t_{OHA}$:地址失效后,数据线上的有效数据维持时间,以保证所读数据可靠。

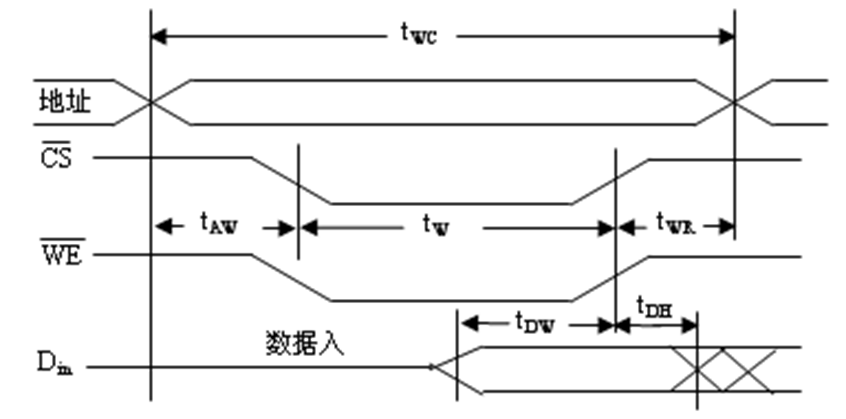

RAM写周期

执行写操作时,必须保证片选信号为低电平,读写信号为低电平。

$t_W$(写入时间):为保证数据可靠地写入,与同时有效的时间必须大于或等于$t_W$。

$t{AW}$(滞后时间):地址有效后,必须经过$t{AW}$时间,WE/信号才能有效(低),否则可能产生写出错。

$t_{WR}$(写恢复时间):WE/无效后,经tWR时间后地址才能改变,否则也可能错误地写入。

$t_{DW}$:写入数据必须在写无效之前tDW时间就送到数据总线上。

$t{DH}$:WE/无效后,数据还要保持的时间。此刻地址线仍有效,$t{WR}>t_{DH}$,以保证数据可靠写入。

$t{WC}$(写周期时间):表示连续两次写操作之间的最小时间间隔。$t{WC} = t{AW} + t_W + t{WR}$。

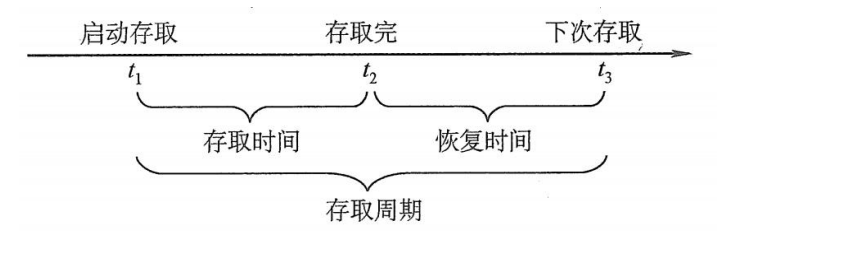

存取时间

存取周期

双端口RAM

双口 RAM 是指一个特殊类型的RAM,它有两套完全独立的数据线、地址线和读 /写控制线。只要不同时访问同一个单元,两个独立的 CPU 可以同时对双口 RAM 进行随机访问。如果同时访问双端口RAM的同一个单元,由内部的控制电路决定哪个端口可以访问该单元。

注意

需要有两组完全独立的数据线、地址线、控制线。CPU、DRAM中也要有更复杂的控制电路

两个端口对同一主存操作有以下4种情况∶

- 两个端口同时对不同的地址单元存取数据。

- 两个端口同时对同一地址单元读出数据。

- 两个端口同时对同一地址单元写入数据。

- 两个端口同时对同一地址单元,一个写入数据,另一个读出数据。

解决方法∶ 置"忙"信号为0,由判断逻辑决定暂时关闭一个端口(即被延时),未被关闭的端口正常访问,被关闭的端口延长一个很短的时间段后再访问。

多模块存储器

传统存储器

多模块存储器

为提高访存速度,常采用多模块存储器,常用的有单体多字存储器和多体并行存储器。

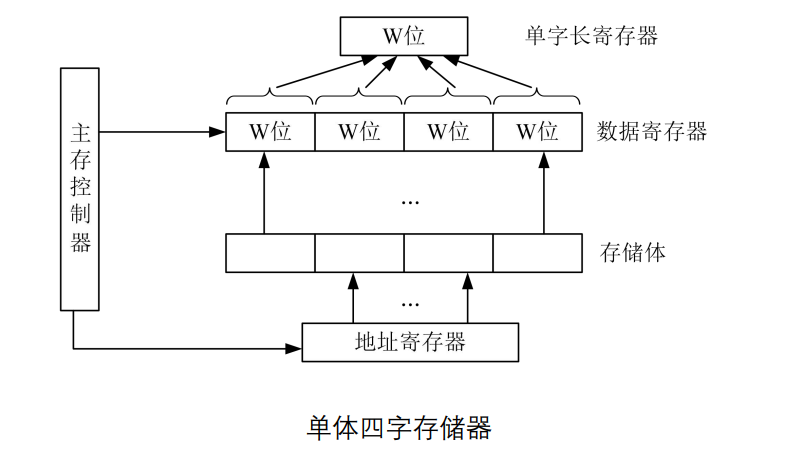

单体多字存储器

单体多字系统的特点是存储器中只有一个存储体,每个存储单元存储 m 个字,总线宽度也为 m 个字。一次并行读出 m 个字,地址必须顺序排列并处于同一存储单元。

eg.单体四字存储器:每字W位,给定一个地址,可以在一个存取周期内读出4×W位指令或数据,使主存带宽提高到4倍

假设存取时间为r,恢复时间为3r那么存取周期为T=4r

特点

- 每个存储单元存储m个字,总线宽度也为m个字,一次并行读出m个字

- 指令和数据在主存内必须是连续存放的

多模块多体并行存储器存储器

多体并行存储器由多体模块组成。每个模块都有相同的容量和存取速度,各模块都有独立的读写控制电路、地址寄存器和数据寄存器。它们既能并行工作,又能交叉工作。

高位交叉编址

高位地址表示体号,低位地址为体内地址。高位交叉编址方式下,总是把低位的体内地址送到由高位体号确定的模块内进行译码。访问一个连续主存块时,总是先在一个模块内访问,等到该模块访问完才转到下一个模块访问,CPU总是按顺序访问存储模块,存储模块不能被并行访问,因而不能提高存储器的吞叶率。

体号 体内地址

低位交叉编址

低位地址为体号,高位地址为体内地址。低位交叉编址方式下,总是把高位的体内地址送到由低位体号确定的模块内进行译码。程序连续存放在相邻模块中。 因此称采用此编址方式的存储器为交叉存储器。采用低位交叉编址后,可在不改变每个模块存取周期的前提下,采用流水线的方式并行存取,提高存储器的带宽。

体内地址 体号