异步fifo深度计算(异步计数状态转换表)

FIFO有同步和异步两种,同步即读写时钟相同,同步FIFO用的少,可以作为数据缓存;异步即读写时钟不相同,异步FIFO可以 解决跨时钟域的问题,在应用时需根据实际情况考虑好fifo深度即可。

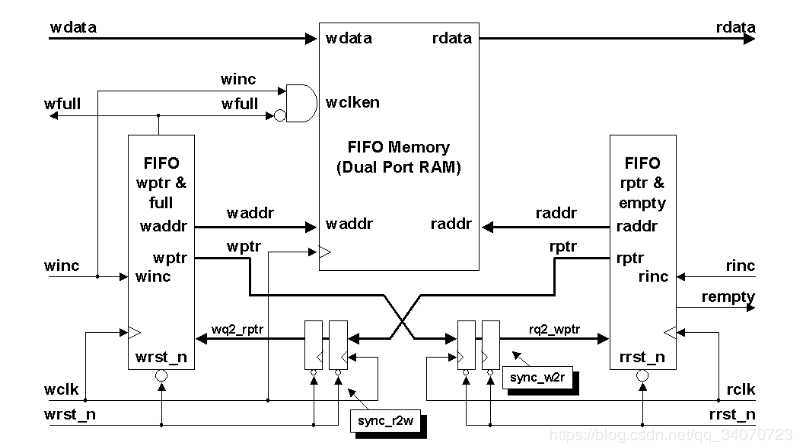

与同步FIFO相同,异步FIFO也主要由五大模块组成,不同的是,异步FIFO的读写逻辑控制还包括了格雷码转换和时钟同步部分:

(1)、 FIFO写逻辑控制——产生FIFO写地址、写有效信号,同时产生FIFO写满、写错等状态信号;

(2)、 FIFO读逻辑控制——产生FIFO读地址、读有效信号,同时产生FIFO读空、读错等状态信号;

(3)、 时钟同步逻辑——通过两级DFF分别将写时钟域的写指针同步到读时钟域,将读时钟域的读指针同步到写时钟域;

(4)、 格雷码计数器——格雷码计数器中二进制计数器的低(n-1)位可以直接作为FIFO存储单元的地址指针;

(3)、 FIFO存储体(如Memory,reg等)。

其逻辑结构如下所示:

计算机组织结构(十一) 总线

📚 文档目录

合集-数的二进制表示-定点运算-BCD 码-浮点数四则运算-内置存储器-Cache-外存-纠错-RAID-内存管理-总线-指令集: 特征- 指令集:寻址方式和指令格式

总线

芯片内部总线

连接芯片的各个部分

例如连接寄存器, ALU和 CPU 的其他部分

通信总线

连接主机和 I/O 设备或者连接不同的计算机系统

系统总线

连接 CPU, 主存, I/O 控制器和其他的功能设备

内容

总线可以分为三种功能组

数据线: 在系统模块之间移动数据. 数据线的数量决定了一次能能够传送的数据的最大容量

FIFO系列(一):FIFO深度计算

当异步FIFO读写端口的throught-put(吞吐量)不同时,会遇到数据丢失的问题,需要考虑FIFO中的深度问题,即为满足读写流畅不卡顿(数据不丢失)时,FIFO的deepth的最小值。

FPGA FIFO深度计算

数字IC设计中我们经常会遇到这种场景,工作在不同时钟域的两个模块,它们之间需要进行数据传递,为了避免数据丢失,我们会使用到FIFO。当读数据的速率小于写数据的速率时,我们就不得不将那些还没有被读走的数据缓存下来,那么我们需要开多大的空间去缓存这些数据呢?缓存开大了会浪费资源,开小了会丢失数据,如何去计算最小FIFO深度是我们讨论的重点。

FIFO深度计算

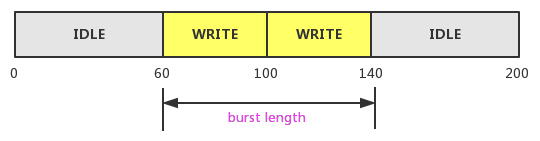

在讲解如何去计算FIFO深度之前,我们来理解一个术语burst length,如果你已经了解了可以跳过。要理解数据的突发长度,首先我们来考虑一种场景,假如模块A不间断的往FIFO中写数据,模块B同样不间断的从FIFO中读数据,不同的是模块A写数据的时钟频率要大于模块B读数据的时钟频率,那么在一段时间内总是有一些数据没来得及被读走,如果系统一直在工作,那么那些没有被读走的数据会越累积越多,那么FIFO的深度需要是无穷大的,因此只有在突发数据传输过程中讨论FIFO深度才是有意义的。也就是说我们一次传递一包数据完成后再去传递下一包数据,我们把一段时间内传递的数据个数称为burst length。在维基百科中,burst transmission是这样解释的:In telecommunication, a burst transmission or data burst is the broadcast of a relatively high-bandwidth transmission over a short period。

Redis 学习笔记 3.4 列表类型

列表类型 (list) 可以存储一个有序的字符串列表,常用的操作是向列表的两端添加元素,或者获得列表的某一个片段。