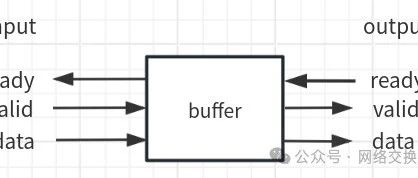

Half-Buffer与Skid-Buffer介绍及其在流水线中的应用

1.问题描述

在介绍skid buffer之前,我们先来假设这样一种情况,在一个多级流水模型之中,比如最为经典的顺序五级流水的处理器模型中,各级之间通过仅通过valid-ready的握手信号进行数据传递,(需要注意的是,这里的输入侧和输出侧的握手信号是不建议直连的,这样不符合流水设计思想的同时,还会加中时序压力)当其中某级发生阻塞的时候,比如lsu的执行访存指令,但是cache未命中,需要从更下级的储存器去请求数据的时候,此时需要通过握手信号来需要阻塞流水线,理所应当的,我们拉低lsu的input_ready信号来阻塞来自上级流水的输入(比如EXU),可是问题是此时上上级(比如IDU)并未被阻塞,还在向上级(EXU)传输数据,同样的情况发生在所有的上游模块。这篇文章便是用来解决上述问题。

“12306”的架构到底有多牛逼?

不仅给出了模拟场景的代码,而且也用压测工具测试了并发情况,是一个很好的学习案例,分享给大家共读。